# Building an Embedded Processor System on a Xilinx Zync FPGA (Profiling): A Tutorial

Embedded Processor Hardware Design *October 6*<sup>th</sup> *2017.*

# **Table of Contents**

| Requirements                                        | 3  |

|-----------------------------------------------------|----|

| Part 1: Building a Zynq-7000 Processor Hardware     | 4  |

| Introduction                                        |    |

| Step 1: Start the Vivado IDE and Create a Project   |    |

| Step 2: Create an IP Integrator Design              |    |

| Customize Instantiated IP                           |    |

| Use Block Designer Assistance                       |    |

| Step 3: Generate HDL Design Files                   |    |

| Step 4: Implement Design and Generate Bitstream     | 16 |

| Step 5: Export Hardware to SDK                      | 18 |

| Export to SDK                                       | 18 |

| Part 2: Build Zynq-7000 Processor Software          | 19 |

| Step 1: Start SDK and Create a Software Application | 19 |

| Step 2: Run the Software Application                |    |

| Add a Breakpoint                                    | 26 |

| Step 3: Executing the Software                      | 27 |

| Part 3: Profiling the Software                      | 29 |

| Step 1: Start SDK and Create a Software Application | 29 |

| Step 2: Profile the Software Application            |    |

| Producing the GMON Executable                       |    |

| Step 3: Generating statistics                       |    |

#### Introduction

This tutorial will guide you through the process of using Vivado and IP Integrator to create a complete Zyng ARM Cortex-A9 based processor system targeting the ZedBoard Zyng development board. You will use the Block Design feature of IP Integrator to configure the Zyng PS and add IP to create the hardware system, and SDK to create an application to verify the design functionality. It will also guide you through the process of profiling an application and analyzing the output.

### **Objectives**

After completing this tutorial, you will be able to:

- Create an embedded system design using Vivado and SDK flow

- Configure the Processing System (PS)

- Add Xilinx standard IP in the Programmable Logic (PL) section

- Use and route the GPIO signal of the PS into the PL using EMIO

- Use SDK to build a software project and verify the functionality in hardware.

- Set up the board support package (BSP) for profiling an application

- Set the necessary compiler directive on an application to enable profiling

- Setup the profiling parameters

#### **Procedure**

This lab is separated into steps that consist of general overview statements that provide information on the detailed instructions that follow. Follow these detailed instructions to progress through the tutorial.

This tutorial comprises three stages (each consisting of steps): You will create a top-level project using Vivado, create the processor system using the IP Integrator, add two instances of the GPIO IP, validate the design, generate the bitstream, export to the SDK, create an application in the SDK, and, test the design in hardware. You will then be able to profile the application and produce statistics that will help you understand the main bottlenecks of your application.

# Requirements

The following is needed in order to follow this tutorial:

- Vivado w/ Xilinx SDK (tested, version 2013.2/version 2014.4). Version 2016.3 could work but with some hiccups.

- Zedboard (tested, **version D**)

# Part 1: Building a Zynq-7000 Processor Hardware

#### Introduction

In this part of the tutorial you create a Zyng-7000 processor based design and instantiate IP in the processing logic fabric (PL) to complete your design. Then you take the design through implementation, generate a bitstream, and export the hardware to SDK.

If you are not familiar with the Vivado Integrated Development Environment Vivado (IDE), see the Vivado Design Suite User Guide: Using the Vivado IDE (UG893).

# Step 1: Start the Vivado IDE and Create a Project

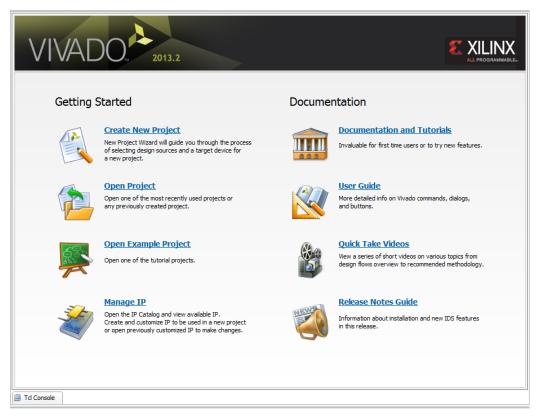

1. Start the Vivado IDE (FIGURE 1) by clicking the Vivado desktop icon or by typing **vivado** at a terminal command line.

Figure 1: Getting Started Page

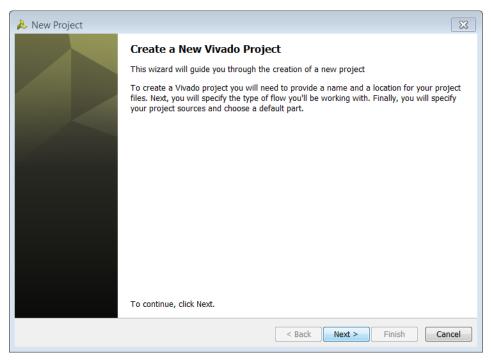

- 2. From the Getting Started page, select **Create New Project**. The New Project wizard opens (FIGURE 2).

- 3. Click Next

Figure 2: Create New Project Wizard

- 4. In the **Project Name** dialog box, type the project name and location. Ensure that **Create project subdirectory** is checked, and then click **Next**.

- 5. In the **Project Type** dialog box, select **RTL Project**, then click **Next**.

- 6. In the **Add Sources** dialog box, ensure that the **Target language** is set to VHDL, then click Next.

- 7. In the **Add Existing IP** dialog box, click **Next**.

- 8. In the **Add Constraints** dialog box, click **Next**.

- 9. In the **Default Part** dialog box select **Boards** and choose "ZedBoard Zyng" Evaluation and Development Kit". Make sure that you have selected the proper Board Version to match your hardware because multiple versions of hardware are supported in the Vivado IDE. Click **Next**.

- 10. Review the project summary in the **New Project Summary** dialog box before clicking **Finish** to create the project.

### **Step 2: Create an IP Integrator Design**

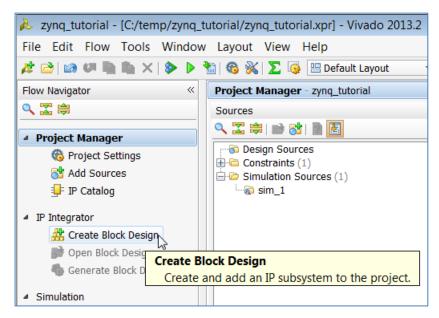

1. In the Flow Navigator, select **Create Block Design** (Fig 3).

Figure 3: Create Block Design from Flow Navigator

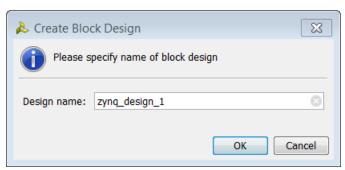

2. In the **Create Block Design** popup menu, specify a name for your IP subsystem design (Figure 4)

Figure 4: Create Block Design Dialog Box

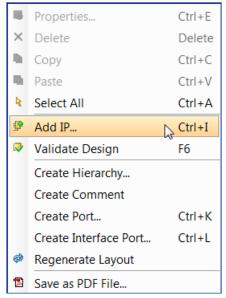

3. Right-click in the Vivado IP integrator diagram window, and select **Add IP**.

Figure 5: Add IP Option

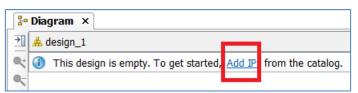

4. Alternatively, you can click the **Add IP** link in the IP integrator diagram area.

Figure 6: Add IP Link in IP Integrator Canvas

The IP Catalog opens.

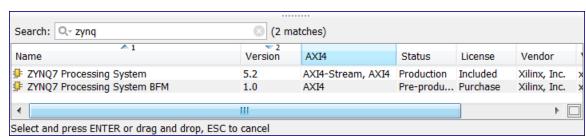

5. In the search field, type **zynq** to find the ZYNQ7 Processing System IP, and then press **Enter** on the keyboard (Fig 7).

Figure 7: The IP Integrator IP Catalog

Because you selected the ZedBoard when you created the project, the Vivado IP integrator configures the design appropriately.

In the Tcl Console, you see the following message:

```

create bd cell -type ip -vlnv

xilinx.com:ip:processing system7:5.2 processing system7 1

INFO: [PS7-6] Configuring Board Preset zed. Please wait .....

```

There is a corresponding Tcl command for all actions performed in the IP integrator block diagram. Those commands are not shown in this document. See the Tcl Console for information on those commands.

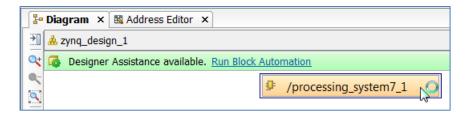

6. In the IP integrator diagram header, click **Run Block Automation**.

Figure 8: Run Block Automation on Zync

The Run Block Automation dialog box opens, stating that the FIXED\_IO and DDR interfaces will be created for the Zyng core.

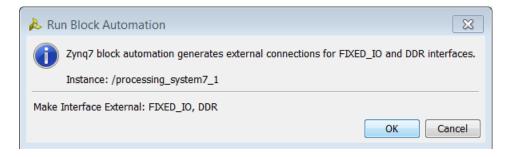

7. Click **OK** (Fig 9).

Figure 9: Zync7 Run Block Automation Dialog Box

After running block automation on the Zynq processor, the IP integrator diagram should look as follows (Fig 10):

Figure 10: Zynq Processing System after Running Block Automation

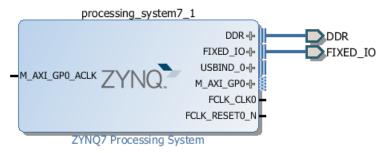

- 8. Now you can add peripherals to the processing logic (PL). To do this, rightclick in the IP integrator diagram, and select Add IP.

- 9. In the search field, type gpi to find the AXI GPIO IP, and then press **Enter** to add the AXI GPIO IP to the design.

- 10. Repeat the action, typing axi bram to find and add AXI BRAM Controller, and typing block to find and add Block Memory Generator.

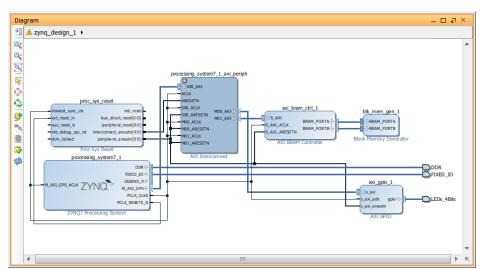

The Block Design window matches FIGURE 11. The relative positions of the IP will vary.

Figure 11: Block Design after Instantiating IP

#### **Customize Instantiated IP**

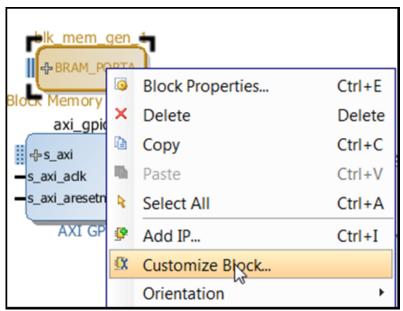

1. Double-click the Block Memory Generator IP, or right-click and select Customize Block (FIGURE 12).

Figure 12: Customize Block Option

The **Re-customize IP** dialog box opens. 2.

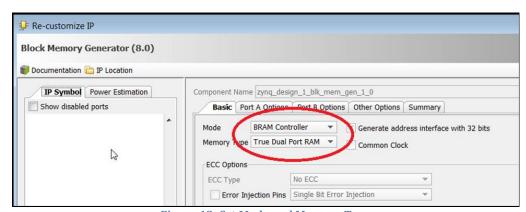

- 2. On the Basic tab of the dialog box, set:

- **Mode** to **BRAM Controller**

- **Memory Type to True Dual Port RAM**

Click **OK** (Fig 13)

Figure 13: Set Mode and Memory Type

The AXI BRAM Controller provides an AXI memory map interface to the Block Memory Generator.

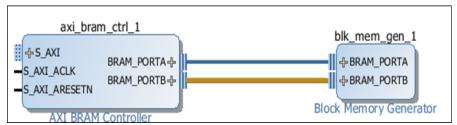

3. Connect the Block Memory Generator to the AXI4 BRAM Controller by clicking the connection point and dragging a line between the IP.

Figure 14: Connected AXI BRAM Controller and Block Memory Generator

The AXI BRAM Controller provides an AXI memory map interface to the Block Memory Generator.

### **Use Block Designer Assistance**

Block Designer Assistance helps connect the AXI GPIO and AXI BRAM Controller to the Zynq-7000 PS.

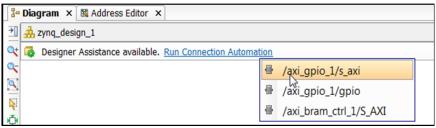

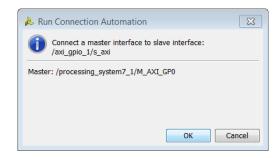

1. Click **Run Connection Automation** and then select /axi\_gpio\_1/s\_axi to connect the BRAM controller and GPIO IP to the Zynq PS and to the external pins on the ZedBoard (FIGURE 15).

**Figure 15: Run Connection Automation**

The Run Connection Automation dialog box opens and states that it will connect the master AXI interface to a slave interface.

In this case, the master is the Zynq Processing System IP (FIGURE 16).

**Figure 16: Run Connection Automation Message**

#### Click OK.

This action instantiates an AXI Interconnect IP as well as a Proc Sys Reset IP and makes the interconnection between the AXI interface of the GPIO and the Zynq-7000 PS.

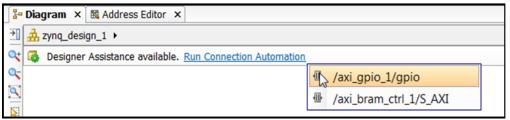

2. Select Run Connection Automation again, and the /axi\_gpio\_1/gpio shown in FIGURE 17.

Figure 17: axi\_gpio Selection

The Run Connection Automation dialog box includes options to hook up to the GPIO port. 4.

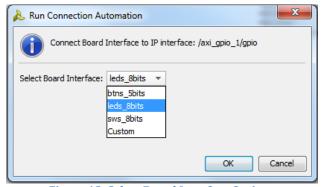

3. Select leds\_8bits (FIGURE 18).

**Figure 18: Select Board Interface Options**

- 4. Click **OK**. This step also configures the IP so that during netlist generation, the IP creates the necessary Xilinx Design Constraints (XDC).

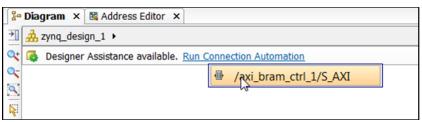

- 5. Click **Run Connection Automation** again, and select the remaining option /axi bram ctrl 1/S AXI (FIGURE 19).

Figure 19: axi\_bram\_ctrl Selection

This completes the connection between the Zynq7 Processing System and the AXI BRAM Controller.

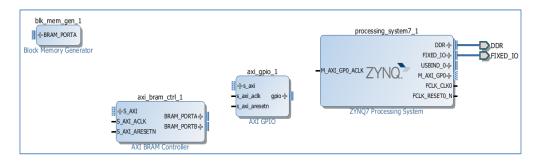

The IP integrator subsystem looks like FIGURE 20. Again, the relative positions of the IP can differ slightly.

Figure 20: Zyng Processor System

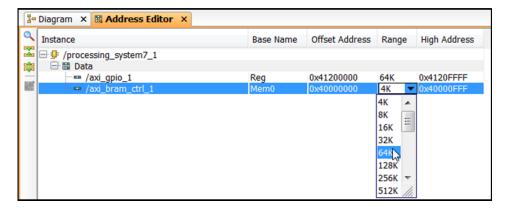

6. Click the Address Editor tab to show the memory map of all the IP in the design.

In this case, there are two IP: the AXI GPIO and the AXI BRAM Controller. The IP integrator assigns the memory maps for these IP automatically. You can change them if necessary.

7. Change the range of the AXI BRAM Controller to **64K**, as shown in FIGURE 21.

Figure 21: axi\_bram\_ctrl to 64k Range

- 8. Save your design by pressing Ctrl-S, or select File > Save Block Design.

- 9. Click the Address Editor tab to make sure that the memory mappings for the GPIO and BRAM controller have been auto populated.

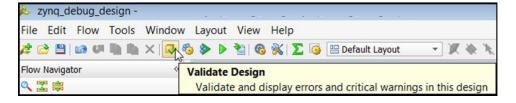

- 10. From the toolbar, run Design-Rules-Check (DRC) by clicking the **Validate Design** button (FIGURE 22). Alternatively, you can do the same from the menu by:

- Selecting **Tools** > **Validate Design** from the menu.

- Right-clicking in the Diagram window and selecting **Validate Design**.

Figure 22: Validate Design Button

The Validate Design Successful dialog box opens (FIGURE 23).

Figure 23: Validate Design Message

#### 11. Click **OK**.

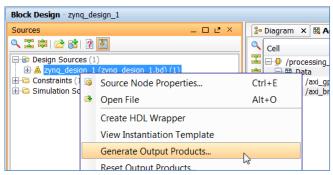

### Step 3: Generate HDL Design Files

You now generate the HDL files for the design.

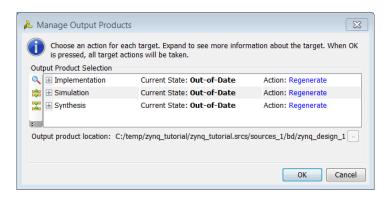

1. In the Source window, right-click the top-level subsystem design and select **Generate Output Products** (FIGURE 24). This generates the source files for the IP used in the block diagram and the relevant constraints file.

**Figure 24: Generate Output Products Option**

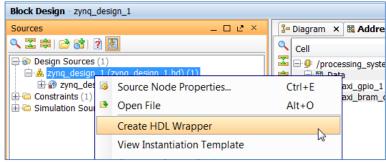

2. The **Manage Output Products** dialog box opens. Click **OK**.

- 3. In the Sources window, select the top-level subsystem source, and select **Create HDL Wrapper** to create an example top-level HDL file (FIGURE 25).

- 4. Click **OK** when the **Create HDL Wrapper** dialog box opens.

Figure 25: Create HDL Wrapper

### **Step 4: Implement Design and Generate Bitstream**

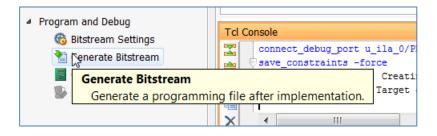

1. In Flow Navigator, click **Generate Bitstream** to implement the design and generate a BIT file.

*Note:* If the system requests to re-synthesize the design before implementing, click **No**. The previous step of saving the constraints caused the flow to mark synthesis out-of-date. Ordinarily, you might want to re-synthesize the design if you manually changed the constraints, but for this tutorial, it is safe to ignore this condition (FIGURE 26).

Figure 26: Generate Bitstream

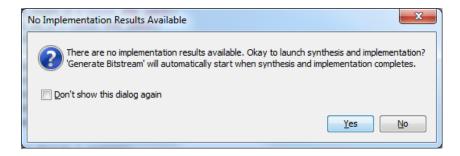

You might see a dialog box stating no implementation results are available.

2. Click **Yes** (Fig 27).

Figure 27: No Implementation Results Available Dialog Box

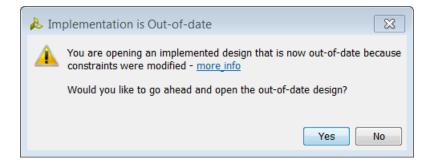

3. After the design implementation, click Open Implemented Design, (FIGURE 28).

**Figure 28: Bitstream Generation Completed**

4. You might get a warning that the implementation is out of date. Click **Yes**.

Figure 29: Implementation Is Out-of-Date Dialog Box

### **Step 5: Export Hardware to SDK**

In this step, you export the hardware description to SDK. You use this in Part 2. The IP integrator block diagram, and the Implemented design, must be open to export the design to SDK.

IMPORTANT: For the Digilent driver to install, you must power on and connect the board to the host PC before launching SDK.

#### **Export to SDK**

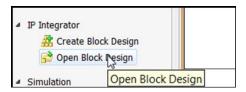

1. In the Flow Navigator, click **Open Block** to invoke the IP integrator design (FIGURE 30).

Figure 30: IP Integrator - Open Block Design

Now you are ready to export your design to SDK.

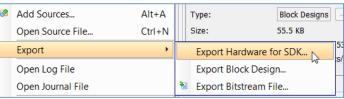

2. From the main Vivado File menu, select Export Hardware for SDK (FIGURE 31).

Figure 31: Export Hardware for SDK

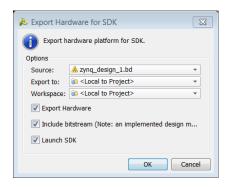

The Export Hardware for SDK dialog box opens, ensure that Export Hardware, Include Bitstream, and Launch SDK are checked (FIGURE 32).

Figure 32: Export Hardware for SDK

# Part 2: Build Zyng-7000 Processor Software

In this portion of the tutorial you will build an embedded software project that prints "Hello World" to the serial port. Connect two micro USB cables to the Zedboard (see Appendix A for more details).

# Step 1: Start SDK and Create a Software Application

- 1. If you are doing this lab as a continuation of Part 1 then SDK should have launched in a separate window (if you checked the Launch SDK option while exporting hardware). You can also start SDK from the Windows Start menu by clicking on Start > All Programs > Xilinx Design Tools > Vivado 2013.2 > SDK > Xilinx SDK 2013.2. When starting SDK in this manner you need to ensure that you in the correct workspace.

- 2. You can do that by clicking on **File > Switch Workspace > Other** in SDK. In the Workspace Launcher dialog box in the Workspace field, point to the SDK\_Export folder where you had exported your hardware. Usually, this is located at

```

..\project name\project name.sdk\SDK\SDK Export.

```

Now you can create a hello world application.

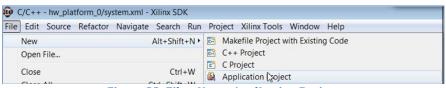

3. Select **File > New > Application Project** (FIGURE 33).

Figure 33: File->New->Application Project

New Project dialog box opens

4. In the Project Name field, type **Zync\_Design**, and click **Next** (FIGURE 34).

Figure 34: SDK Application Project

5. From the Available Templates, select Hello World (FIGURE 35) and click Finish.

Figure 35: SDK New Project Template

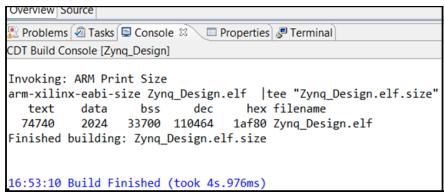

When the program finish compiling, you will see the following (FIGURE 36).

Figure 36: SDK Message

# **Step 2: Run the Software Application**

Now, you must run the hello world application on the ZedBoard. Make sure that your hardware is powered on and a USB Cable is connected to the host PC. Also, ensure that you have a USB cable connected to the UART port of the ZedBoard. Please check Appendix A, and Appendix B for more guidelines

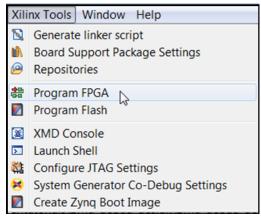

1. Download the bitstream into the FPGA by selecting Xilinx **Tools > Program FPGA** (FIGURE 37).

Figure 37: Program FPGA

This opens the Program FPGA dialog box.

2. Ensure that the path to the bitstream that you created in this tutorial is correct and then click **Program**.

**Note**: The DONE LED on the board turns blue if the programming is successful.

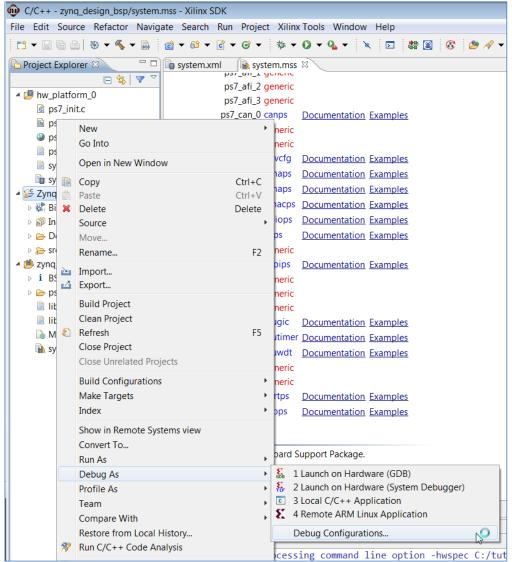

- 3. Select and right-click the **Zynq\_Design** application.

- 4. Select **Debug As** and **Debug Configurations** (FIGURE 38).

Figure 38: Launch on Hardware

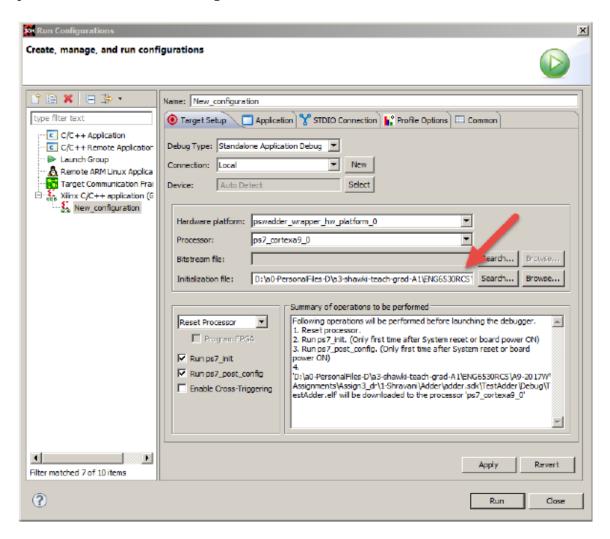

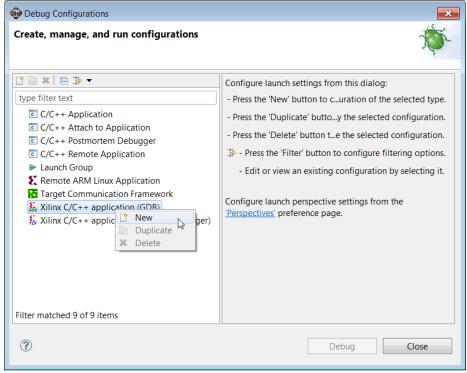

5. In the Debug Configurations dialog box, right-click Xilinx C/C++ Application (GDB) and select New.

Figure 39: Debug Configuration Dialog Box

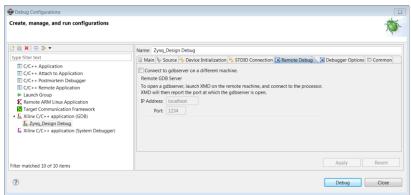

6. In the Debug Configurations dialog box, click **Debug**.

**Figure 40: Run Debug Configurations**

7. The Confirm Perspective Switch dialog box opens. Click **Yes**.

**Figure 41: Confirm Perspective Switch Dialog Box**

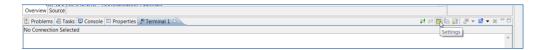

8. Set the terminal by selecting the Terminal 1 tab and clicking the Settings button (FIGURE 42).

**Figure 42: Settings Button**

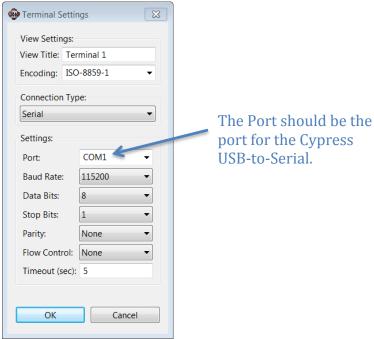

9. Use the following settings for the ZedBoard (FIGURE 43). Click **OK**.

**Figure 43: Terminal Settings**

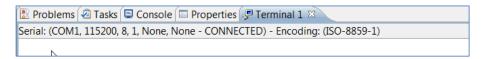

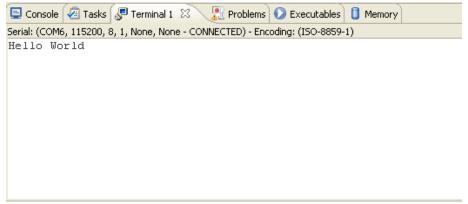

10. Verify the **Terminal** connection by checking the status at the top of the tab (FIGURE 44).

**Figure 44: Terminal Connection Verification**

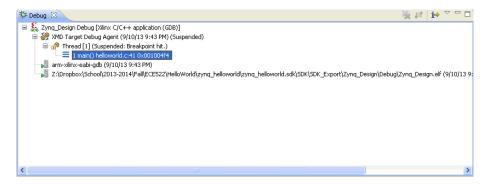

11. In the **Debug** tab, expand the tree, and select the processor core on which the program is to be run (FIGURE 45.

**Figure 45: Processor Core to Debug**

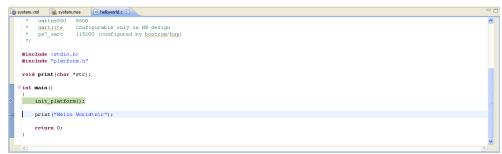

12. If it is not already open, select .../src/helloworld.c, line 41, and double click that line to open the source file.

### Add a Breakpoint

You add a breakpoint on line 43.

1. Select **Navigate > Go To Line** (FIGURE 46).

Figure 46: Go to Line

- 2. In the Go To Line dialog box, type **43**.

- 3. Double click on the left pane of line 43, which adds a breakpoint on that line of source code (Figure 47).

Figure 47: Add a Breakpoint

# **Step 3: Executing the Software**

This step will take you through executing the code up to and past the break point.

- 1. Click the **Resume** button or press **F8**

- 2. Click the **Step Over** button or press **F6**

- 3. You should see "Hello World" in the terminal if everything worked correctly (FIGURE 48).

Figure 48: Terminal Output

### **Export the Design to the SDK**

Step 1

- 1-1. Export the design to the SDK, create the software BSP using the standalone operating system; Enable the profiling options.

- 1-1-1. Export the hardware configuration by clicking File > Export > Export Hardware

- **1-1-2.** Tick the box to *Include Bitstream*, and click **OK**

- 1-1-3. Launch SDK by clicking File > Launch SDK and click OK

- 1-1-4. In SDK, select File > New > Board Support Package.

- 1-1-5. Notice Standalone\_bsp\_0 in the Project name field and click Finish with default settings.

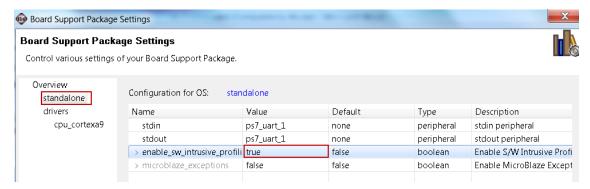

A Board Support Package Settings window will appear.

1-1-6. Select the Overview > standalone entry in the left pane, click on the drop-down arrow of the enable sw intrusive profiling Value field and select true.

Figure 3.1 Enable profiling in the board support package

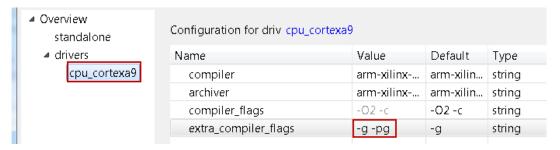

Select the Overview > drivers > cpu\_cortexa9 and add -pg in addition to the -g in the extra\_compiler\_flags Value field.

Figure 3.2 Adding profiling switch

**1-1-8.** Click **OK** to accept the settings and create the BSP.

# **Create the Application**

Step 2

- 2-1. Create the tutorial application.

- 2-1-1. Select File > New > Application Project.

- Enter tutorial-profile as the project name, select the Use existing standalone\_bsp\_0 option, and click Next.

- **2-1-3.** Select **Hello World** in the *Available Templates* pane and click **Finish**.

- Replace the Hello World C program with the intended application you have. 2-1-4.

- 2-2. A snippet of the source code is shown in the following figure.

```

m.hdf ⊠ 🙀 system.mss 📔 helloworld.c 🗵

#include_manameters.h

void CallFunBig()

j=0;

print("Hello Fun Big\n\r");

for (i=0;i<=800000;i++)

++j;

printf("j=%d\n\r",j);

void CallFunMedium()

**j;

printf("j=%d\n",j);

void CallFunSmall()

int i.i:

j=0;

print("Hello Fun Small\n\r");

for (i=0;i<=200000;i++)</pre>

++j;

printf("j=%d\n",j);

int main()

init_platform();

print("Hello from main\n\r");

CallFunBig();

CallFunMedium();

CallFunSmall();

cleanup_platform();

return 0;

```

Figure 3.3 Adding profiling switch

2-2-1. Save the program and it should compile successfully and generate the tutorial-profile.elf file.

### **Run the Application and Profile**

Step 3

- 3-1. Place the board into the JTAG boot up mode. Program the PL section and run the application.

- 3-1-1. Place the board in the JTAG boot up mode. Check Appendix A for Zedboard connection.

- **3-1-2.** Power ON the board. (Check Appendix B for some information).

- 3-1-3. Select Xilinx Tools > Program FPGA and click on Program.

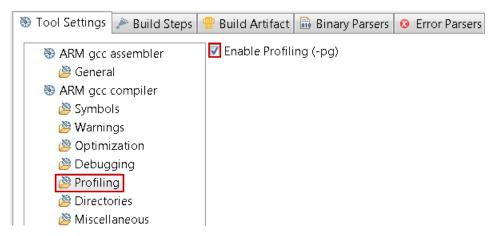

- **3-1-4.** Right click on the tutorial-profile *directory*, and select **C/C++ Build Settings**.

- 3-1-5. Under the ARM gcc compiler group, select the Profiling sub-group, then check the **Enable Profiling** box, and click **OK**.

Figure 3.4 Compiler setting for enabling profiling

- **3-1-6.** From the menu bar, Select Run > Run Configurations... and double click on Xilinx C/C++ application to create a new configuration.

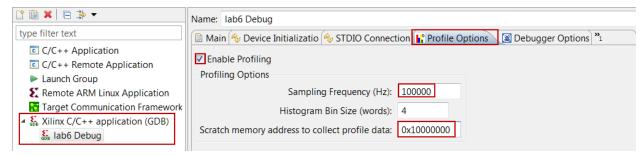

- 3-1-7. Click on the newly created tutorial-profile Debug configuration, and select the Profile Options tab.

- 3-1-8. Click on the Enable Profiling check box, enter 100000 (100 kHz) in the Sampling Frequency field, enter 0x10000000 in the scratch memory address field, and click Apply.

Figure 3.5 Profiling options

**3-1-9.** Click the **Run** button to download the application and execute it.

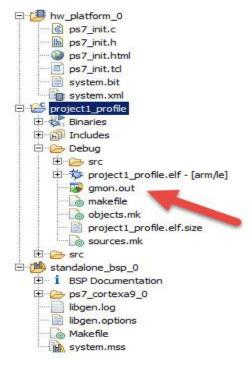

The program will run, and when execution has completed, a message will be displayed indicating that the profiling results are being saved in gmon.out file at the tutorial-profile\Debug directory.

- 3-1-10. Click OK.

- 3-2. Invoke gprof and analyze the results.

- **3-2-1.** Expand the *Debug* folder under the **tutorial-profile** project in the Project Explorer view, and double click on the gmon.out entry.

Figure 3.6 Invoking gprof on gmon.out

3-2-2. The Gmon File Viewer dialog box will appear showing tutorial-profile.elf as the corresponding binary file. Click OK.

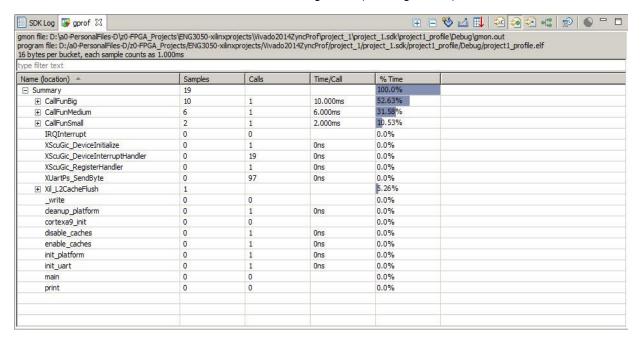

**3-2-4.** Click in the **%Time** column to sort in the descending order (See Figure 3.7).

Figure 3.7 Sorting results

- Go back to the Run Configuration, and change the sampling frequency to 1000000 (1 MHz) and profile the application again.

- 3-2-6. Invoke gprof, select the Sorts samples per function output, and sort the %Time column.

Notice that the output has better resolution and reports more functions and more samples per function calls.

- 3-2-7. Close the SDK and Vivado programs by selecting File > Exit in each program.

- **3-2-8.** Turn OFF the power on the board.

#### Conclusion

This Tutorial led you through enabling the software BSP and the application settings for the profiling.

### APPENDIX A (Zedboard Connection)

As seen in the Figure below, connect the Zedboard with two micro USB cables.

- 1. The first cable to the JTAG micro USB port

- 2. The second cable to the UART port.

Also make sure that Jumpers 7,8,9,10,11,12 are connected to GND.

#### APPENDIX B

Also, when starting SDK make sure that the processor can be reset by including the ps\_init file as shown in the Figure below.